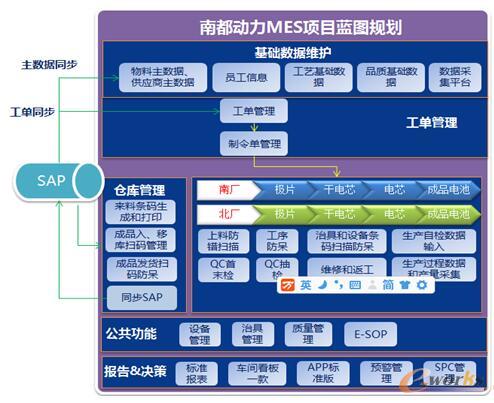

基于Quartus Prime Standard 18.0的FPGA基礎開發流程詳解

FPGA(現場可編程門陣列)開發是一個將硬件描述語言(HDL)轉化為可在特定芯片上運行的數字電路的過程。Intel Quartus Prime Standard Edition 18.0是一款功能強大且廣泛使用的FPGA開發軟件。本文將詳細介紹使用該軟件進行基礎FPGA開發的標準流程。

第一步:需求分析與設計規劃

在打開軟件之前,必須明確設計目標。例如,是創建一個簡單的計數器、狀態機還是接口控制器?確定輸入輸出信號、時鐘頻率、資源估算等。這一階段通常用文本或框圖完成,是后續所有工作的基礎。

第二步:創建新項目

1. 啟動Quartus Prime 18.0。

2. 點擊“File” -> “New Project Wizard”。

3. 指定項目目錄、項目名稱和頂層設計實體名稱(通常與項目名一致)。

4. 添加已有的設計文件(如.v或.vhd源文件)。如果新建項目,此步可跳過,后續再添加。

5. 選擇目標FPGA器件家族、具體型號和封裝。這是關鍵一步,需與開發板匹配。

6. 選擇第三方綜合、仿真工具(如有),然后完成向導。

第三步:設計輸入 - 編寫源代碼

這是核心步驟,即使用硬件描述語言(如Verilog HDL或VHDL)描述電路功能。

- 點擊“File” -> “New”,選擇“Design Files”下的“Verilog HDL File”或“VHDL File”。

- 在打開的編輯器中編寫代碼。例如,一個簡單的Verilog模塊可能包括模塊聲明、輸入輸出端口定義、寄存器與線網聲明以及功能描述(行為級或結構級)。

- 保存文件,并確保文件名與模塊名一致(

.v為后綴)。

第四步:分析與綜合

此步驟將HDL代碼轉換為門級電路網表,并檢查語法和基本邏輯錯誤。

- 在“Processing”菜單下,點擊“Start” -> “Start Analysis & Synthesis”。

- 軟件會在“Tasks”窗口和“Messages”窗口顯示進度和報告。任何錯誤或嚴重警告都需要在此階段解決。

第五步:引腳分配與約束

告訴編譯器設計中的邏輯端口對應到FPGA芯片的哪個物理引腳。

- 點擊“Assignments” -> “Pin Planner”。

- 在彈出的界面中,根據開發板原理圖,在“Location”列為每個輸入輸出信號指定具體的引腳編號。

- 還可以通過“Assignment Editor”設置時序約束(如時鐘頻率)。

第六步:完整編譯

這是最耗時的步驟,包括綜合、布局布線、時序分析和生成編程文件。

- 點擊“Processing” -> “Start Compilation”,或工具欄的紫色三角形圖標。

- 編譯成功后,會生成一個

.sof(SRAM對象文件)用于后續下載,并會提供資源利用率、時序性能等詳細報告。務必查看“Timing Analyzer”報告,確保設計滿足時序要求(如無時序違例)。

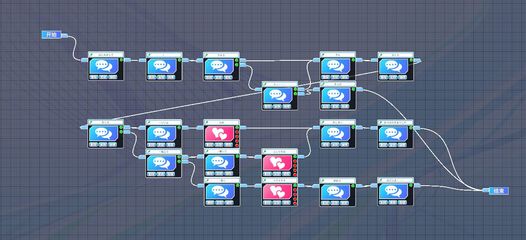

第七步:仿真驗證(可選但強烈推薦)

在下載到板卡前,通過仿真驗證邏輯功能是否正確。Quartus Prime自帶仿真工具(University Program IP或與ModelSim協同)。

- 創建測試平臺文件(Testbench)。

- 配置仿真工具,指定測試平臺為頂層。

- 運行仿真,觀察波形圖,驗證輸出是否符合預期。

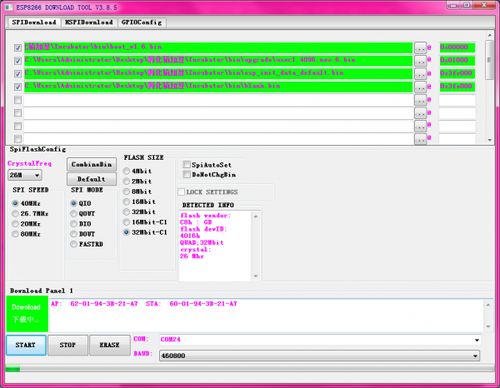

第八步:程序下載與配置

將編譯生成的配置文件下載到FPGA開發板。

- 連接好JTAG或USB-Blaster下載線,給開發板上電。

- 點擊“Tools” -> “Programmer”。

- 確保硬件被識別,然后添加生成的

.sof文件。 - 勾選“Program/Configure”,點擊“Start”。進度條完成后,設計即被加載到FPGA中運行。

第九步:在線調試與驗證

使用Quartus Prime的SignalTap II Logic Analyzer工具,可以實時捕獲FPGA內部信號,就像在芯片內嵌入了一個邏輯分析儀,這對于調試復雜設計極其有用。

****

基于Quartus Prime Standard 18.0的FPGA基礎開發流程是一個從抽象設計到物理實現的系統化工程。遵循“設計-綜合-實現-驗證”的迭代過程,并充分利用軟件提供的分析和調試工具,是成功完成FPGA項目開發的關鍵。隨著項目復雜度增加,還需要掌握更高級的約束設置、IP核集成和系統級設計方法。

如若轉載,請注明出處:http://www.0ayu.cn/product/66.html

更新時間:2026-03-21 23:16:28